- Create the Xilinx environment

source /tools/Xilinx/Vivado/2018.3/settings64.sh- build your bitstream

make clean; make- Program FPGA

make program_fpga- In

script.pychange the USB port according to the correct one (usels -l /dev/ttyUSB*to find it out) - Running the script

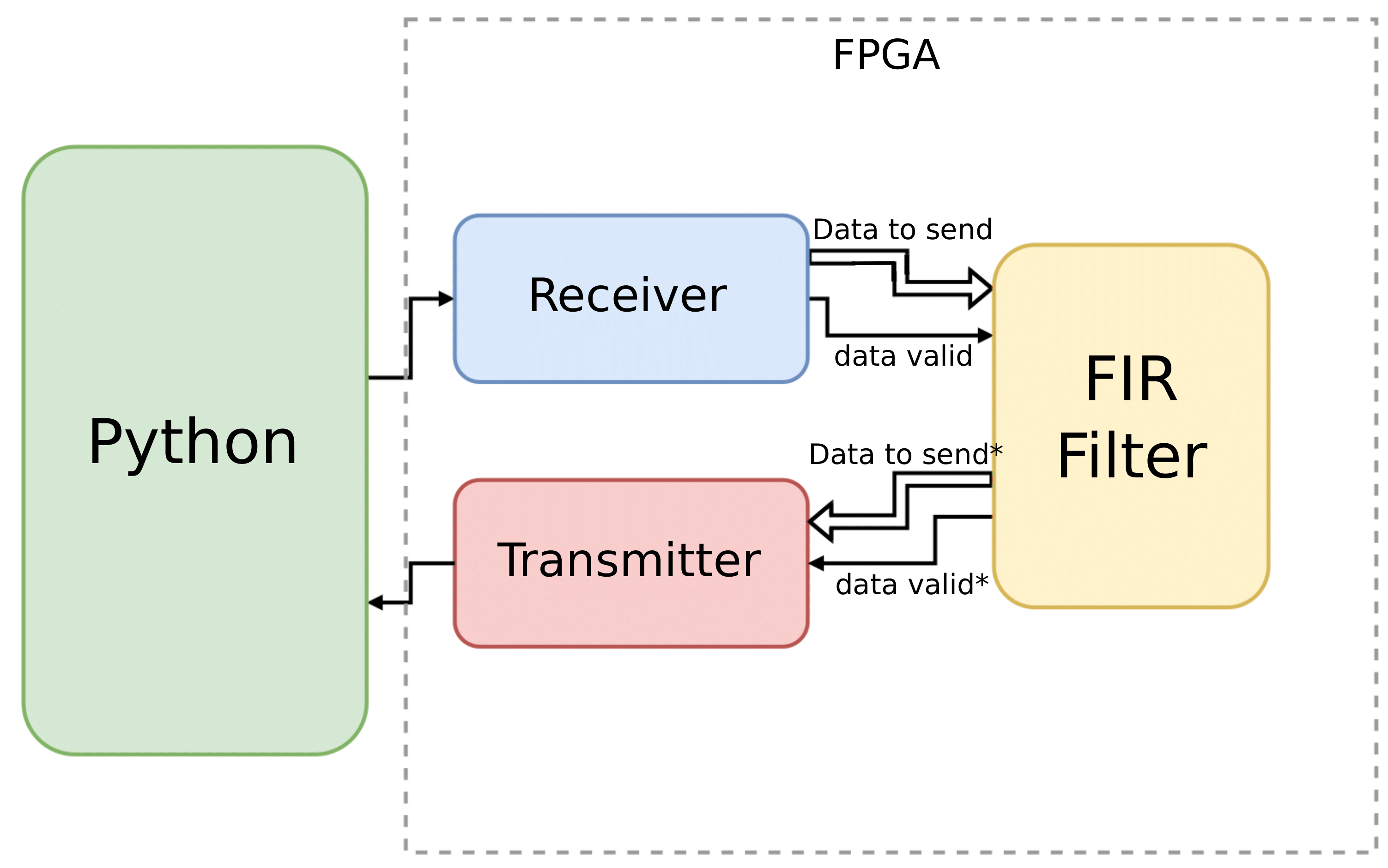

script.py, the signal present insignal.txtwill be sent to the FPGA and filtered - After compilation, the filtered signal will be in

fromfpga.txt

A brief explanation of how the filter was made can be found in the report.